|

Reg istered SDRAM在MPC8241系统中的应用

摘要 介绍Registered SDRAM的工作原理和接口芯片,以及在MPC8241嵌入式系统中进行Registered SDRAM电路设计的实例;给出电路原理设计和PCB布局布线的一般规则。

关键词 RegisteredSDRAM MPC8241 接口技术

在嵌入式系统中,传统的SDRAM接口电路设计模式是系统主控芯片直接驱动所有内存芯片的地址/控制信号。当内存芯片数量较多时,这类直接驱动的设计会出现因主控芯片的地址/控制信号驱动能力不足,而导致系统内存工作不稳定的问题。Registered SDRAM是指具有地ti/控制信号锁存电路的SDRAM模块,特点是系统主控芯片的地址/控制信号不直接驱动内存芯片,而是通过地址/控制信号锁存电路驱动内存芯片的地址/控制信号。Registered SDRAM模式降低了主控制芯片地址/控制信号直接驱动的逻辑门数,同时提高了系统SDRAM接口电路的负载能力。当系统的内存芯片数量较多时,Regis_tered SDRAM是一种较好的设计方法。

1 Reqistered SDRAM的工作原理

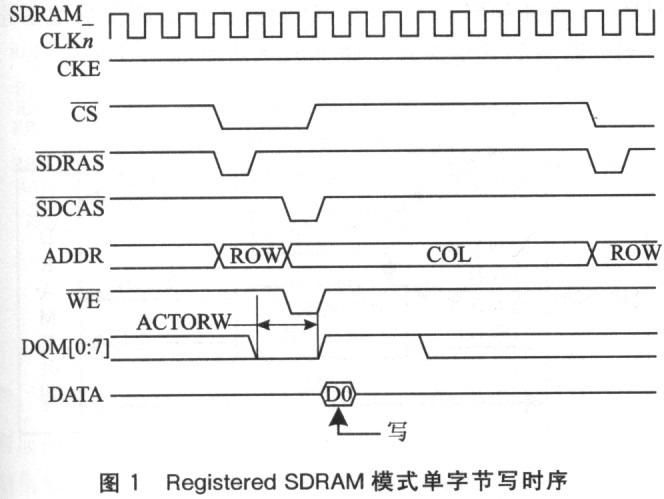

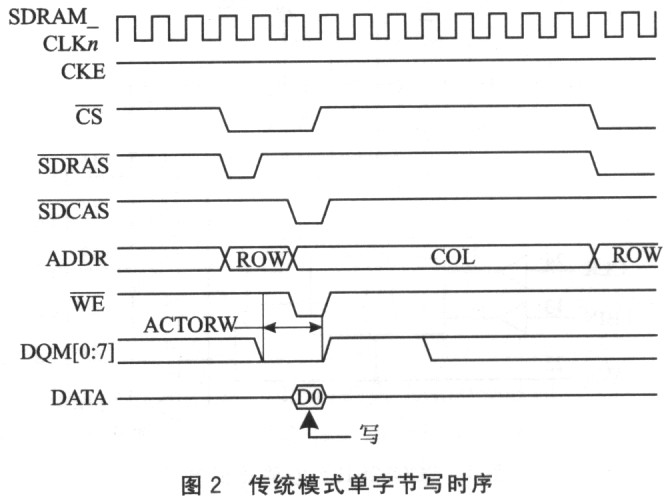

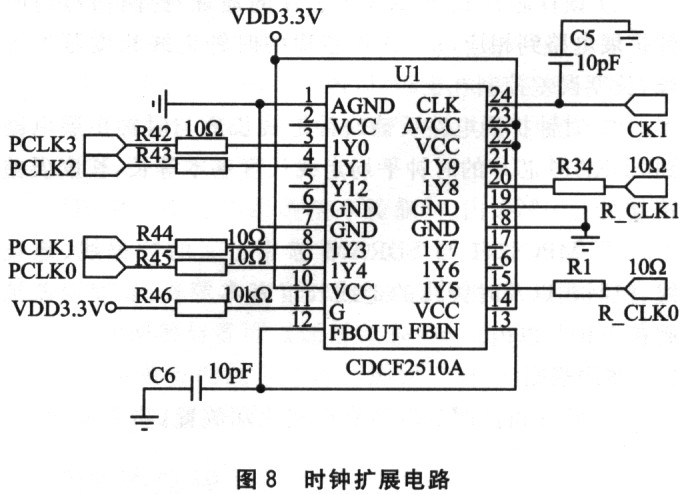

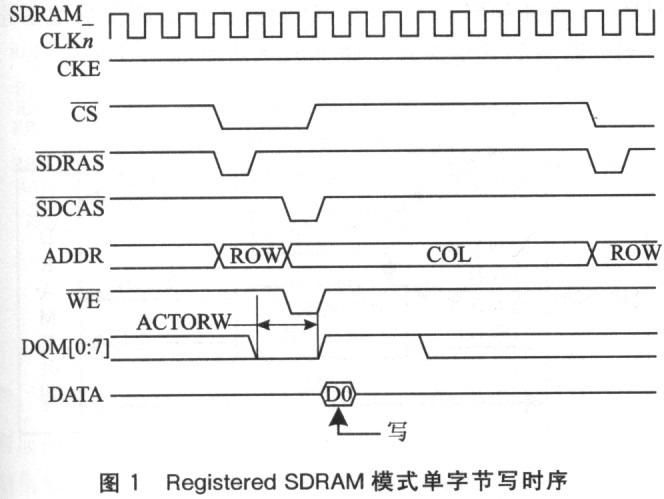

在Registered SDRAM模式下,当主控芯片对SDRAM芯片进行访问时,数据总线信号(DATA)要比传统模式多延迟一个时钟周期。以主控芯片对SDRAM芯片进行单字节写时的操作时序为例,对两种模式进行对比说明,其他时序的对比不再详述。

对比图1、图2的时序可知,在主控芯片对SDRAM总线发起操作(以CS、CDRAS同时为低电平的时刻为发起时间)到数据总线(DATA)的信号(DO)有效期间,传统模式为2个时钟周期,Registered SDRAM模式为3个时钟周期。Registered SDRAM模式在硬件电路上采用地址/控制信号,要先经过锁存电路的锁存再延迟一个时钟周期输出的方法,消除这一时钟周期的差异。

典型Registered SDRAM接口电路由二部分组成:地址/控制信号锁存电路与时钟扩展电路。地址/控制信号锁存电路通常由2片多通道D触发锁存芯片构成。该电路将主控芯片SDRAM接口的控制信号(CS,DQM[O:7],SDRAS,SDCAS。CKE,WE)和地址信号(ADDR)进行锁存,并将锁存后输出的信号与所有内存芯片相对应的地址/控制信号输入端连接。锁存时钟由时钟扩展电路产生。在锁存时钟的上升沿对地址/控制信号进行锁存。地址/控制信号锁存电路的另一功能,是对主控芯片与SDRAM芯片之间的连接进行电气隔离,使主控制芯片地址/控制信号直接驱动的逻辑门数得到降低,从而提高系统SDRAM接口电路的驱动能力。

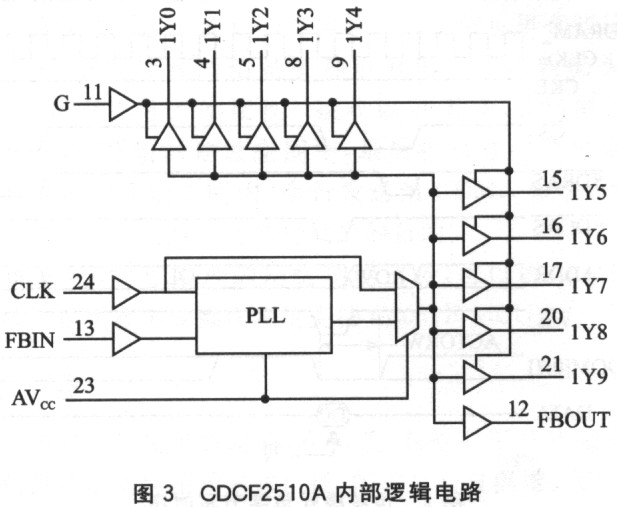

时钟扩展电路的功能是对主控制芯片输出的SDRAM时钟进行扩展,即将输入的一路SDRAM时钟信号,扩展为多路同频时钟输出。其中一路输出时钟作为反馈时钟,反馈给时钟扩展芯片的反馈时钟输入端;另外两路输出时钟作为地址/控制信号锁存电路的锁存时钟,分别驱动2片锁存芯片;其他输出时钟分别输出给不同的SDRAM芯片。原则上,每片SDRAM芯片均有独立的输入时钟。在时钟扩展电路中,可以通过调节各时钟的对地由容值.对各时钟间的相关系进行调整。

对SDRAM芯片而言,Registered SDRAM模式的操作时序与传统模式的操作时序是等同的。这是因为在Regigtered SDRAM模式下,虽然数据信号较地址/控制信号延迟1个时钟周期,但因地址/控制信号要先经过锁存电路的锁存再延迟1个时钟周期输出,因此数据信号与地址/控制信号能同时有效到达SDRAM芯片。这一能同时有效到达的特性与传统模式的时序特性是相同的。

2 Registered SDRAM接口电路芯片简介

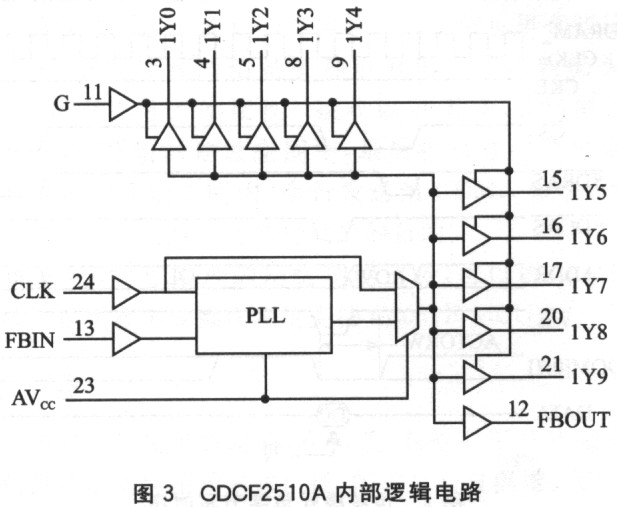

2.1 CDCF2510A

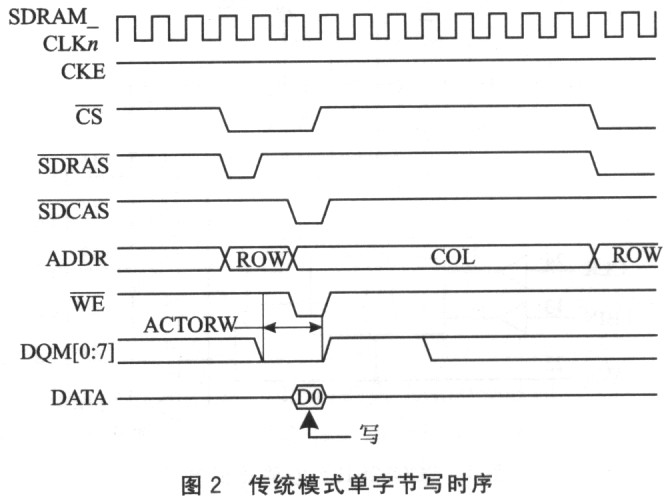

CDCF2510A为TI公司生产的低skew(skew<±125ps)、低抖动(jitte_cyc_cyc<士70 ps)的PLL时钟驱动器。工作频率范围为25~140 MHz。可将1路输入时钟扩展为10路同频输出时钟,同时具有输出时钟反馈功能。该芯片主要用于SDRAM接口的时钟扩展。芯片的内部逻辑电路如图3所示。

图3所示的CLK为输入时钟;1Y0~1Y9为10路输出扩展时钟;FBOUT、FBIN分别为反馈时钟的输出脚与输入脚;G为扩展时钟输出允许控制脚,高电平有效。

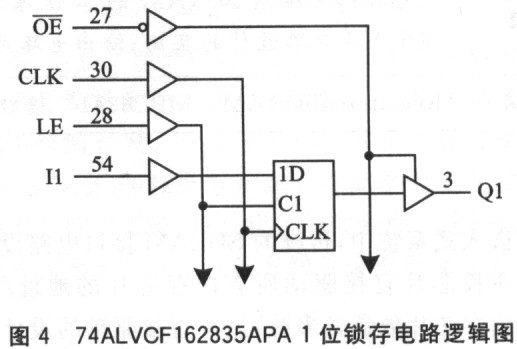

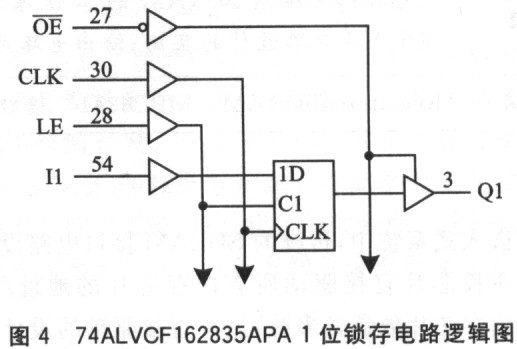

2.2 74ALVCF 162835APA

74ALVCFl62835APA为多通道D锁存器。设计采用Fairchild公司的产品。该芯片可同时锁存18位的输入信号。在供电电压为3.O~3.6 V时,锁存延迟tpd(CLK锁存开始到数据输出有效的时间)最大为3.7 ns。

3 Registered SDRAM在MPC8241嵌入式系统中的设计实现

MPC8241为摩托罗拉公司生产的较高性能32位嵌入式CPU,内部主要集成了32位PCI总线接口,SDRAM接口以及可与Flash芯片或简单逻辑接口芯片(如UART控制芯片)等连接的外围总线。其SDRAM接口可工作于多种模式。本设计采用Registered SDRAM模式且对系统提供128 MB内存,设计的SDRAM时钟为1OO MHz。

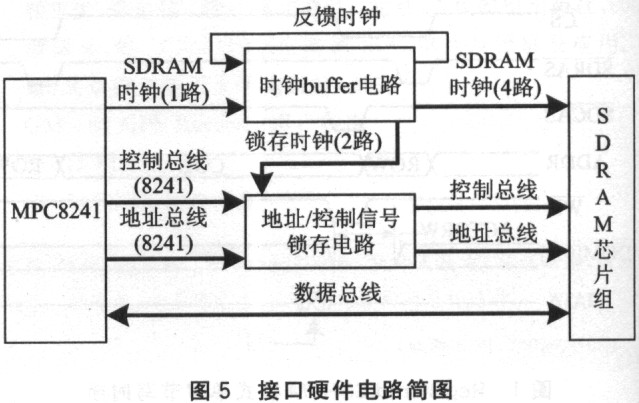

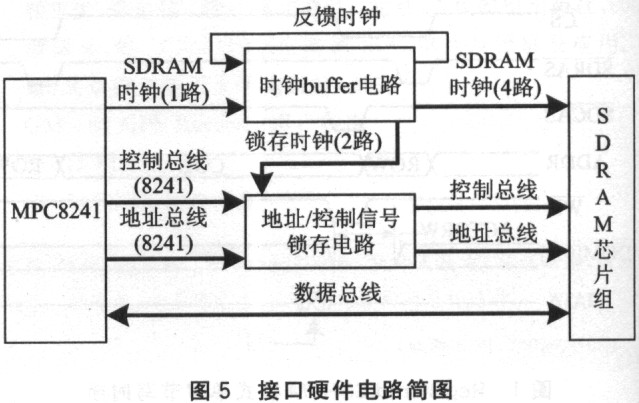

对128 MB的内存,因MPC8241的SDRAM接口数据总线宽度为64位,所以采用4片16M×16数据位的内存芯片,且芯片直接贴装在PCB板上的方式实现。100MHz时钟由.MPC8241产生,经时钟扩展电路扩展之后连接到电路中的其他芯片。硬件电路简图如图5所示。

图5中的内存接口电路由二部分组成:地址/控制信号锁存电路与时钟扩展电路。

3.1 地址/控制信号锁存电路

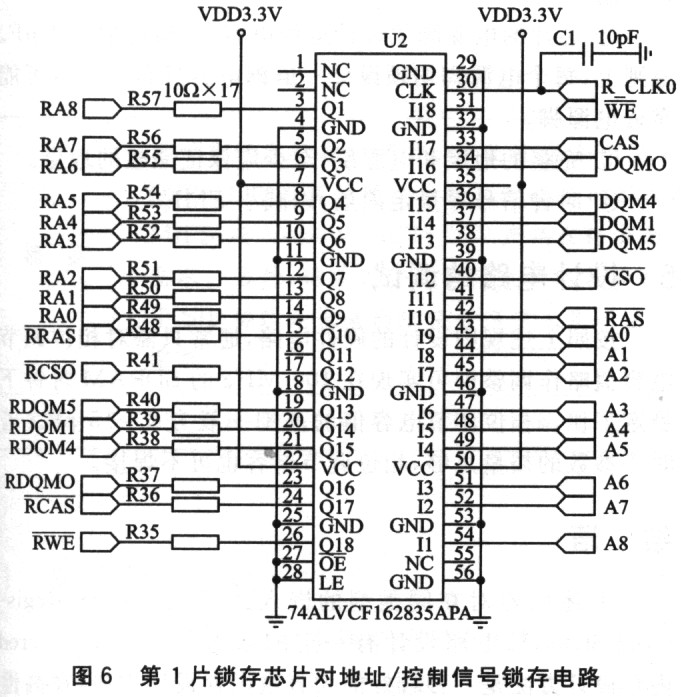

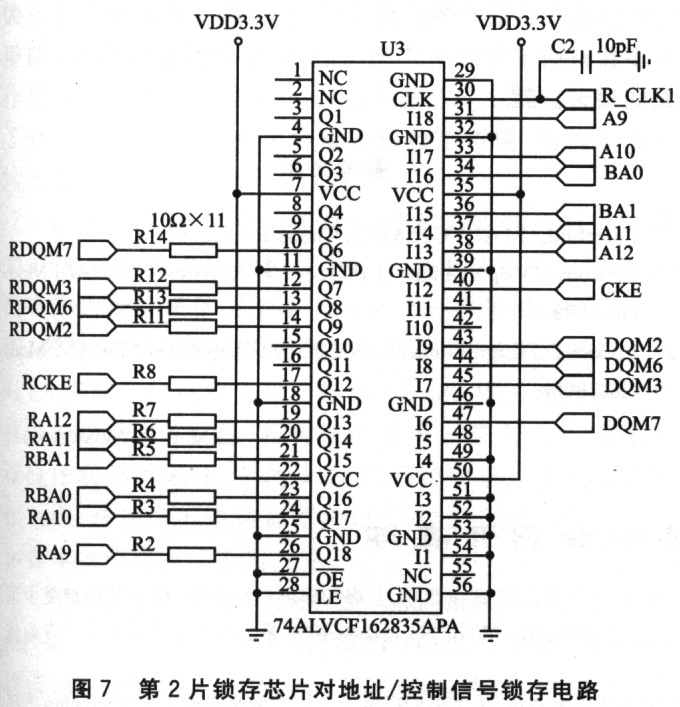

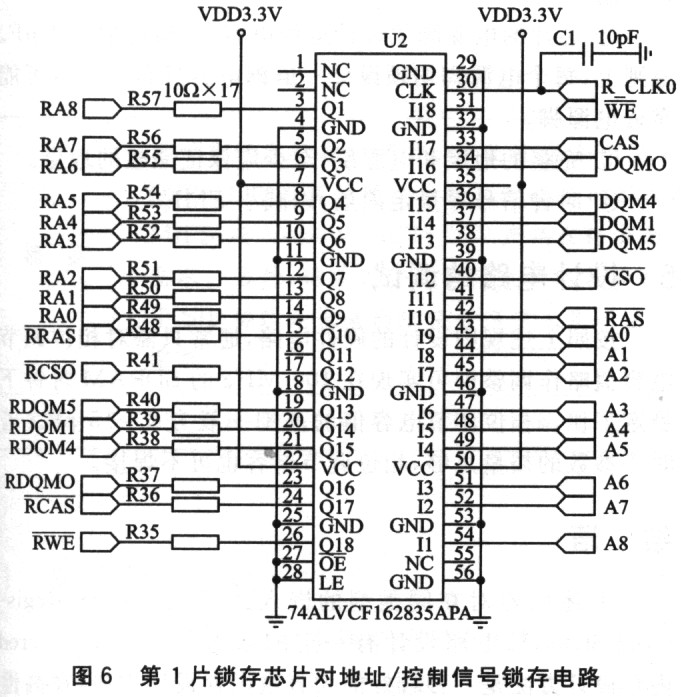

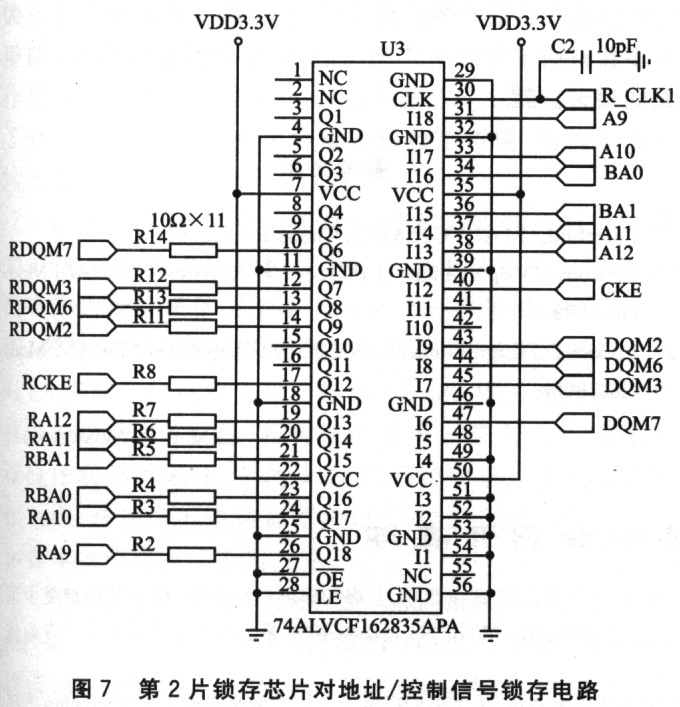

该电路是将MPC824l的SDRAM接口输出地址信号和控制信号利用2片74ALVCFl62835APA进行锁存,并将锁存输出信号与所有内存芯片对应脚连接。2片锁存芯片的设计电路如图6、图7所示。

在图6和图7中,U2与U3的右侧信号与MPC8241对应信号相连接,左侧的信号与4片内存芯片的地址/控制信号引脚连接。U2与U3分别利用锁存时钟R_CLK0和R_CLKl的上升沿对输入信号进行锁存。2片锁存芯片的OE、LE脚均设计为低。

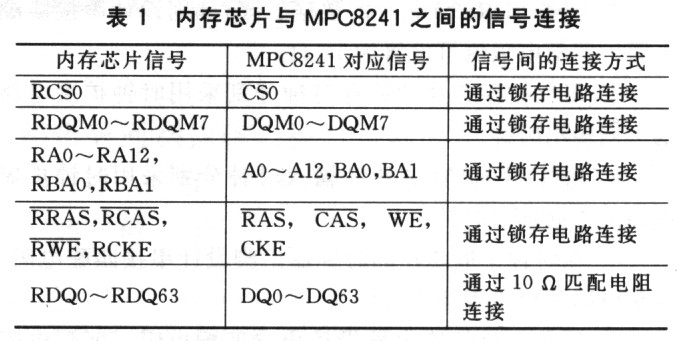

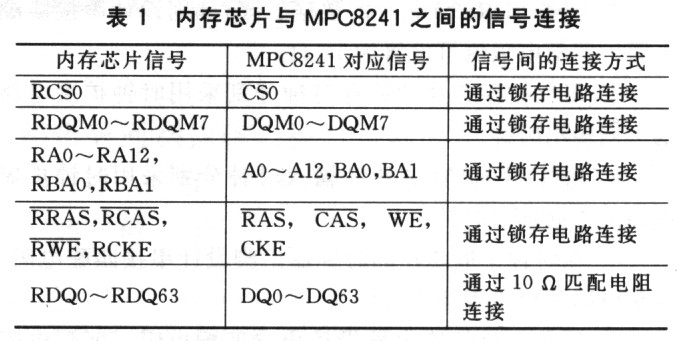

内存芯片与MPC8241之间的信号连接如表1所列。

在电路设计时,信号(RCSO、RAO~RAl2、RBA0、RBAl、RRAS、RCAS、RWE、RCKE)与所有内存芯片对应引脚连接。数据信号RDQ0~RDQ63以8位为一组分配给4片内存芯片。

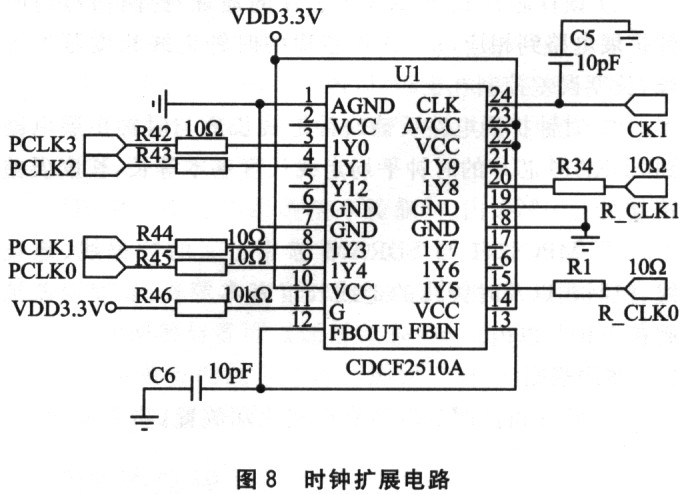

3.2时钟扩展电路

时钟扩展电路如图8所示。该电路将MPC8241输出的SDRAM时钟信号CKl通过时钟扩展芯片(CDCVF25I0A)进行同频时钟扩展,即将l路SDRAM时钟信号CKl扩展为6路时钟输出。其中4路输出时钟(PCLK0~PCLK3)分别输出给4颗内存芯片。另外2路时钟(R_CI,K0,R_CLKl)分别与2片锁存芯片的锁存时钟输入脚连接,作为地址/控制信号锁存电路的锁存时钟;同时,输出反馈时钟与芯片时钟反馈输入端连接。

4 原理设计与布局布线规则

与传统的SDRAM接口电路相比.Registered SDARM电路对线路电气参数的设计约束相对宽松,设计时基本不用考虑主控芯片的驱动能力;但因Registered SDRAM也是较高速的接口电路,因此其电路设计也应遵循一定的规则,以保证设计电路的可靠性和稳定性。

(1)原理设计规则

①在各芯片的时钟输入端设计相位调节电容,电容值可设置为10pF,可根据实测数据调整。

②在各SDRAM芯片的数据引脚,分别设计串接匹配电阻。匹配电阻值可设置为l0Ω。

③每片锁存芯片的锁存时钟分别采用时钟扩展电路的不同输出时钟。

④每片SDRAM芯片的输入时钟分别采用时钟扩展电路的不同输出时钟。

⑤在时钟扩展芯片的时钟输出脚设计串接匹配电阻。匹配电阻值可设置为l0Ω。

⑥锁存芯片的输出端设计串接匹配电阻。匹配电阻值可设置为lOΩ。

(2)布线规则

①SDRAM数据线:MPC824l到同-SDRAM芯片的数据信号走线需要进行等长控制,长度误差控制在士5%之内。

②SDRAM地址/控制线:锁存芯片到同-SDRAM

芯片的地址/控制信号走线需要进行等长控制,长度误差控制在士5%之内。

③时钟扩展电路输出到锁存芯片的2路锁存时钟,其走线需要进行等长控制,长度误差控制在士l.27mm之内。

④时钟扩展电路输出到SDRAM芯片的4路时钟,其走线需要进行等长控制,长度误差控制在士l.27 mm之内。

⑤锁存芯片到SDRAM芯片的地址/控制信号与时钟扩展电路到相应SDRAM芯片的时钟走线长度基本等长,长度误差控制在±5%以内。

⑥时钟扩展电路反馈时钟走线长度与时钟扩展电路到SDRAM芯片的时钟平均走线长度基本等长,长度误差控制在士l0%以内。

⑦MPC824l与SDRAM芯片之间的数据线、地址线、控制线以及时钟线的走线长度基本等长,长度误差控制在±10%以内。

(3)布局规则

①所有相位调节电容靠近接收端放置。

②所有时钟串接匹配电阻靠近发送端放置。

③SDRAM芯片数据引脚的串接匹配电阻靠近SDRAM芯片。

④锁存芯片输出端的串接匹配电阻靠近输出端放置。

(4)其他设计规則

①各走线须进行阻抗控制,即单端线按50Ω阻抗进行控制。

②芯片的电源脚须设汁退耦电容,容值可取O.1μF。原则上,每个电源脚均须设计一退耦电容且布局时尽可能靠近电源脚。

③完整的地层和电源层,至少应保证完整的地层。

④时钟信号尽量走内层,以减小EMI。

5 设计电路的调试

按照上述规则设计的硬件电路,通常只需对相位调节电容值略作调整即可实现在100 MHz的SDRAM时钟下稳定工作。相位调节电容值的范围一般为5~15pF。若时序参数的裕量足够,相位调节电容也可不焊接。

结 语

上述内容对在同类型的嵌入式系统中进行Regis-tered SDRAM电路设计有一定的参考价值。Registered内存设计方法是一种较好的大容量内存设计方法,在高性能计算机上已经得到广泛应用,但在嵌入式系统中还不为大多数科研工作者所熟悉。这里,推荐给各位同行,期望共同探讨。

| 会员服务热线: |

深圳矽通科技版权所有 © Copyright 2005-2007, ic-cn.com.cn All Right Reserved. |

|

深 圳:13410210660 QQ : 317143513  |

|

客服联系: MSN:CaiZH01@hotmail.com E-mail:CaiZH01@163.com |

|

|