|

基于FPGA的HDLC转E1传输控制器的实现

摘 要:本文介绍了一种用FPGA实现的HDLC转E1的协议控制器,能实现将速率为N×64Kbps(N=1~124)的HDLC数据分接至M路(M=1~4)E1信道中传输,并允许各路E1的最大时延为64ms。讨论了E1帧结构设计和系统的FPGA实现方法。

关键词: 帧结构;HDLC;E1;FPGA

引言

E1是我国电信传输网一次群使用的传输标准,由于我国的E1资源十分丰富, 这样的传输路径非常容易获得,灵活利用现有丰富的E1信道来传输HDLC数据,可以节约大量传输成本。通常,一路HDLC数据仅通过一路E1信道传输,但是如果HDLC数据的速率很大,一路E1信号的带宽不足以传输,那么HDLC数据就要分接到M路E1信道中传输,接收端再把M路E1信号合路恢复出HDLC数据,M路E1信号如果传输路径不同,肯定会导致不同的延迟,本系统设计时,允许各路E1信号的最大延迟为64ms。

系统E1帧结构设计

本系统中的E1码流的帧结构可以参照CCITT G.732、G.704或G.706建议给出的PCM基群30/32路系统帧结构得到,但又有所不同。

信息位的组成

本系统所要传输的净负荷(信息位)是N×64Kbps的HDLC数据,标准E1中的TS16信令时隙与TS1~TS15及TS17~TS31共31个时隙可以传送净负荷。所以,N和M满足关系式N≤31×M。对于最大情况,即N=124,M=4时,净负荷占用31个时隙。当N<124,以至不能填满所有31个时隙,则固定填入无效位‘1’。

TS0时隙的设计

考虑到系统要能实现将一路N×64Kbps的HDLC数据按比特分接在M路E1信道中独立传输,并在接收端通过合路正确恢复出此数据,合路过程要求M路E1信号完全同步,而实际线路中各路之间有不同程度的延迟,这就要求系统具有延时缓冲能力。在此期间利用一个存储器对数据进行缓冲保存。而为了辨别某一路保存在SRAM中的CRC复帧应该和其它路保存在SRAM中的相应CRC复帧合路,即为了实现复帧同步,就需要对每一个CRC复帧加上标号,也就是加上复帧定位码。此外,由于HDLC数据是按比特分接在M路E1信道中传输的,当M=2,3,4时,那么在接收端就必须按照发送时分接的顺序将M路E1信道中的信息位按比特复接成HDLC数据。所以各路E1都需要一个代表分/复接顺序的路标号。为了充分利用E1信道资源 ,利用E1奇帧帧头后三个备用比特为用户提供一个12Kbps的同步数据通道,也可以作为低速的异步数据通道,如常用的2400、4800、9600bps的RS-232信号。

系统设计

硬件设计

系统的硬件部分包括一片FPGA和一块SRAM,FPGA选用ALTERA公司Cyclone系列EP1C6。Cyclone系列器件是低价格,中等密度的FPGA,内部有5980个逻辑单元,20个4Kbit的RAM块和2个内部锁相环。

由于系统允许各路E1信道可以有最大64ms的延时,一个复帧周期为2ms,即最大延迟为32个复帧时间。一个复帧由16个基本帧组成,32个复帧的的比特数为32×256×16=128Kbit,那么各路需要RAM的最大容量为128Kbit。由于最大路数M=4,所以系统所需的RAM最大容量为4×128Kbit= 512Kbit。而EP1C6内部只有80Kbit的RAM,所以选择使用外接RAM的方法,本系统选用Inbond公司的W24L01,其容量为1024Kbit。

通过VHDL实现系统功能

系统采用自顶向下的EDA设计流程,利用VHDL语言编程实现系统功能。

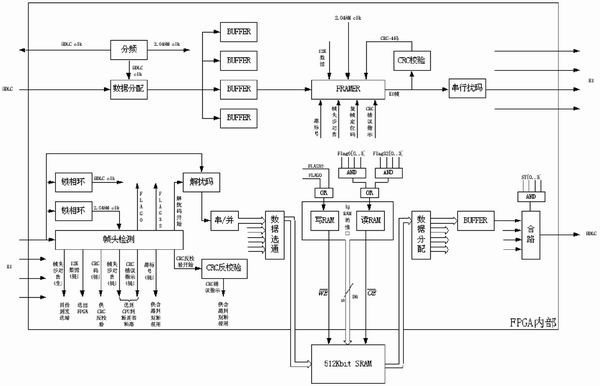

发送部分主要由锁相环模块、分路模块、成帧模块、CRC校验模块和串行扰码模块组成。在主时钟模式下,由本地晶振经有理数分频产生N×64KHz时钟和2.048MHZ时钟,N×64KHz时钟作为HDLC数据的时钟产生源,N×64Kbps的HDLC先经过串/并转换,并写到M个缓存器中,然后用2.048MHZ时钟读出,并将其插入到E1帧相应的时隙中,组成M路E1信号,并经过CRC-4校验,最后经过串行扰码,发送出去。在从时钟模式下,N×64KHz时钟由HDLC提供,2.048MHZ时钟由锁相环模块从N×64Kbps的HDLC中提取。时钟模式的选择及M、N的数值都可以在FPGA内部通过VHDL语言编程设定。

接收部分包括锁相模块、帧头检测模块、解扰码模块、读写RAM模块以及合路模块。在接收部分,先用锁相环通过输入的E1信号锁出2.048MHZ的同步时钟和N×64KHz时钟,用2.048MHZ的时钟对E1信号进行帧头检测,找到帧头后,系统进入帧同步状态,然后解扰码,CRC反校验,以及提取其它各种控制信息和数据。解扰码以后的数据经串/并转换后输出FPGA,存到片外RAM中。收到控制信息后,FPGA开始从RAM中读取数据,并在N×64KHz时钟的控制下进行并/串转换,去帧头,最后合成一路N×64Kbps的HDLC输出信号。

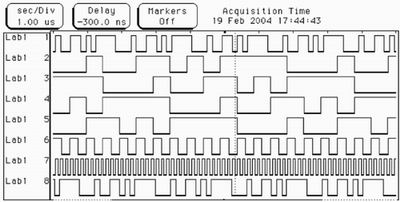

图1 仿真波形图

仿真与测试

对整个系统和每个子模块都进行了功能仿真和后仿真。功能仿真平台为ModelSim + 5.5f ,综合平台为FPGA Express 3.5,后仿真平台为ALTERA Quartus3.0。用逻辑分析仪HP54645D实测波形如图1所示(取M=4,N=104)。

结语

通过对FPGA进行VHDL编程,实现了将速率为N×64Kbps (N=1~124)的HDLC数据按比特分接至M路(M=1~4)E1信道中传输,并充分利用E1奇帧的TS0时隙,为用户提供12Kbps的同步数据传输通道,而且允许各路E1有64ms的时延。本文设计的HDLC转E1传输控制器也可以作为其它协议转换器的一个过渡桥梁。例如可以将10Base-T的以太网信号,先经过以太网转HDLC协议控制器(如ADMTEK公司生产的ADM6993芯片),然后通过HDLC转E1传输控制器,从而实现了ETHERNET over TDM的功能。

| 会员服务热线: |

深圳矽通科技版权所有 © Copyright 2005-2007, ic-cn.com.cn All Right Reserved. |

|

深 圳:13410210660 QQ : 317143513  |

|

客服联系: MSN:CaiZH01@hotmail.com E-mail:CaiZH01@163.com |

|

|